集成了ARM Cortex-M0内核微处理器的电容式触摸感应芯片的集成电路设计

随着物联网、智能家居和便携式设备的飞速发展,对高性能、低功耗且集成度高的微控制器需求日益增长。其中,集成了ARM Cortex-M0内核的微处理器,因其出色的能效比、精简的指令集和成熟的生态系统,已成为嵌入式系统设计的理想选择。当此类内核与先进的电容式触摸感应技术结合,形成一颗专用的电容式触摸感应处理器芯片时,便能创造出高度集成、响应灵敏且用户友好的智能交互解决方案。本文将探讨这类芯片的集成电路设计关键考量。

一、 核心架构与系统集成

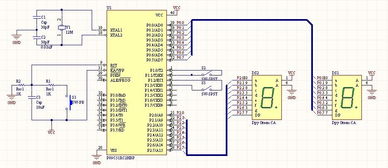

设计的核心是ARM Cortex-M0处理器。它是一个32位精简指令集(RISC)内核,具有低功耗、小硅片面积和高代码效率的特点。在芯片设计中,Cortex-M0作为主控制器,负责执行触摸感应算法、处理外部中断、管理通信接口(如I2C、SPI、UART)以及控制其他外设。

围绕该内核,需要集成一系列专用和通用功能模块:

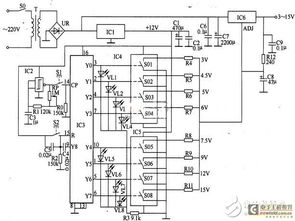

- 电容式触摸感应前端:这是芯片的“感官”部分。通常包括多个高灵敏度、低噪声的电容传感通道(对应多个触摸按键、滑条或滚轮)。前端电路负责将微小的电容变化(由手指触摸引起)转换为可测量的电信号(如电压或频率变化)。

- 模拟-数字转换器:一个高精度、低功耗的ADC(模数转换器)至关重要,用于将模拟传感信号数字化,供Cortex-M0内核进行算法处理。通常采用逐次逼近型或Σ-Δ型ADC以满足精度和噪声抑制要求。

- 数字信号处理单元:虽然Cortex-M0可以运行软件算法,但为了进一步降低CPU负载和功耗,有时会集成专用的硬件协处理器或状态机,用于执行基础的滤波、基线跟踪和阈值比较等重复性任务。

- 存储器:集成适量的Flash存储器(用于存储固件代码)和SRAM(用于程序运行和数据缓存),容量根据应用复杂度和通道数量确定。

- 电源管理单元:为实现低功耗运行,尤其是电池供电场景,需要一个高效的PMU。它应支持多种工作模式(如运行、睡眠、深度睡眠),并能动态调节内核、外设和传感电路的电压与时钟频率。

- 时钟系统与复位电路:提供稳定的系统时钟(可能包括内部RC振荡器和外部晶体振荡器接口)以及可靠的上下电复位和看门狗功能。

- 通用输入输出与通信接口:提供丰富的GPIO,部分可复用于触摸通道;集成标准通信接口,便于与主控MCU或传感器网络连接。

二、 电容传感关键技术设计

- 传感方案选择:常见方案有电荷转移、电容数字转换和弛张振荡等。设计需权衡灵敏度、响应速度、抗噪声能力和功耗。例如,CDC方案能提供高分辨率的数字电容值,但功耗可能较高;而弛张振荡方案结构简单、功耗低,适合对成本敏感的应用。

- 噪声抑制与抗干扰:电容传感极易受到电源噪声、射频干扰和环境温湿度变化的影响。设计时必须考虑:

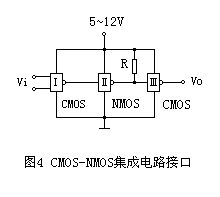

- 硬件层面:采用差分传感结构、屏蔽驱动技术、优化的PCB布局与走线(在芯片封装和系统应用层面)、内部电压稳压和滤波电路。

- 软件/算法层面:由Cortex-M0运行先进的数字滤波算法(如中值滤波、均值滤波)、自适应阈值算法和环境补偿算法,以区分真实触摸和噪声。

- 灵敏度与功耗平衡:更高的灵敏度意味着能检测更轻微或带手套的触摸,但通常伴随着更高的传感电路功耗和更易受噪声影响。设计需要通过可编程配置(如调整采样率、激励电流或积分时间),让用户能根据具体应用场景(如家电面板、可穿戴设备)进行优化。

三、 低功耗设计策略

低功耗是此类芯片的核心竞争力之一。策略包括:

- 动态功耗管理:Cortex-M0内核本身支持睡眠模式。芯片设计应允许在无触摸时,CPU和大部分外设进入休眠,仅由低功耗传感电路或定时器周期性唤醒进行扫描。

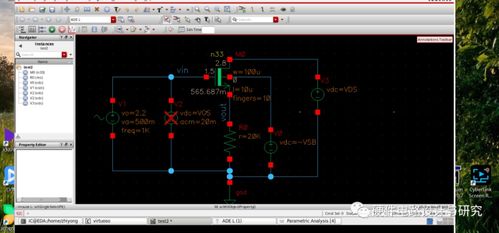

- 模拟电路优化:采用亚阈值设计技术、关断闲置通道电源、使用开关电容等低功耗电路结构来构建传感前端和ADC。

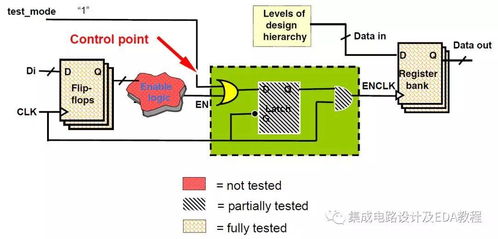

- 时钟门控与电源门控:在寄存器传输级设计时,对不工作的模块关闭时钟和电源,显著降低静态和动态功耗。

四、 设计流程与验证挑战

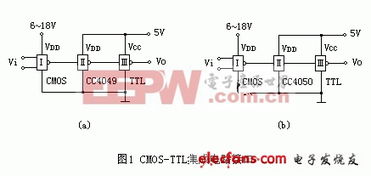

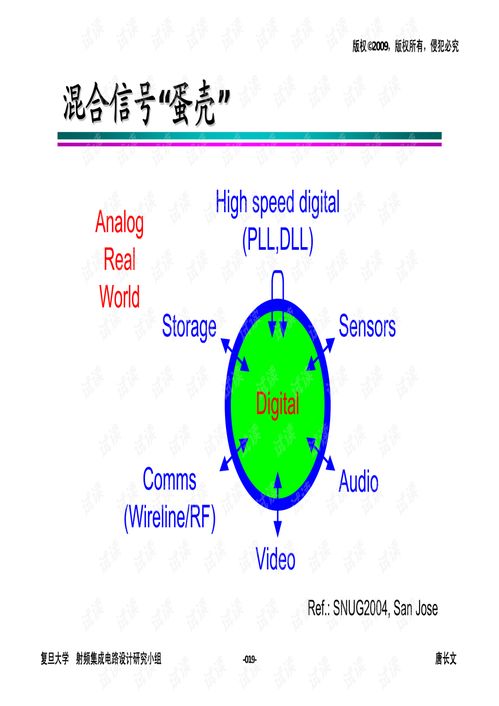

此类芯片设计遵循典型的混合信号IC设计流程,但挑战突出:

- 混合信号协同设计与仿真:需要精确建模模拟传感电路、ADC与数字处理器(Cortex-M0及其外设)之间的交互。使用混合信号仿真工具确保信号完整性和系统功能正确。

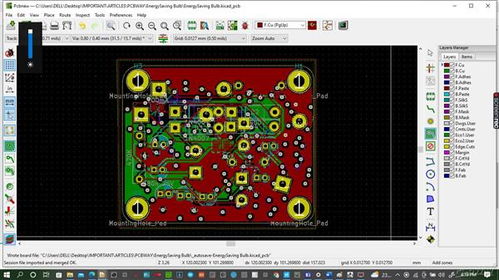

- IP集成与验证:ARM Cortex-M0是一个软核或硬核IP。集成时需确保其与片上总线(如AHB/APB)、存储器控制器及自定义外设的正确连接和时序收敛。

- 抗静电与可靠性:作为用户接口芯片,必须满足严格的ESD(静电放电)和EMC(电磁兼容性)标准,这需要在芯片I/O设计和系统级防护上投入大量精力。

- 固件与硬件协同开发:触摸性能极大依赖于算法。需要在设计早期就开展硬件-软件协同验证,使用FPGA原型或仿真模型来开发和优化触摸感应固件库。

五、 应用与展望

集成了Cortex-M0的电容触摸处理器芯片,凭借其高集成度、优异性能和灵活可编程性,已广泛应用于智能家电控制面板、消费电子(手机、平板配件)、工业HMI、汽车中控以及智能物联网设备。随着工艺进步和AIoT发展,此类芯片的设计将朝着更高集成度(集成更多传感器、无线连接)、更强AI处理能力(在边缘端运行更复杂的触摸手势识别算法)和超低功耗的方向持续演进。

设计一颗成功的集成ARM Cortex-M0的电容式触摸感应芯片,是一个系统工程,需要在处理器架构、模拟混合信号电路设计、低功耗技术和系统级应用之间取得精妙平衡,最终为用户带来无缝、可靠且节能的触控体验。

如若转载,请注明出处:http://www.datiantongchen.com/product/46.html

更新时间:2026-04-20 06:29:54