三位数字显示电容测试表电路设计详解

三位数字显示电容测试表是一种用于精确测量电容值的电子仪器,其核心在于将待测电容的容量值转换为可被数字电路处理和显示的标准信号。本文将围绕其系统架构、关键集成电路设计以及工作流程进行详细阐述。

一、 系统总体架构

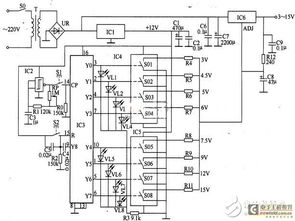

该电容测试表通常由以下几个核心模块构成:

- 电容-频率/时间转换电路:这是测量的核心。常见方案是利用待测电容(Cx)构成振荡器(如555定时器构成的多谐振荡器)或单稳态触发器。电容值的变化直接改变输出脉冲的频率或宽度。例如,在单稳态模式下,输出脉冲的宽度 T = k R Cx(k为常数,R为基准电阻),从而将电容值转换为时间信号。

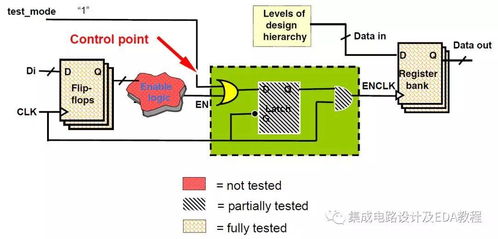

- 时基与控制逻辑电路:产生精确的闸门时间(如100ms),用于控制对转换后脉冲信号的计数时间。此部分通常由晶体振荡器、分频器及逻辑门电路构成,确保测量周期的准确性。

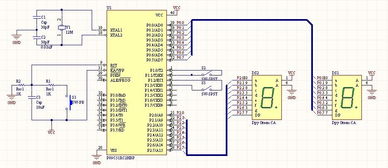

- 计数与锁存电路:在闸门时间内,对电容-频率转换电路输出的脉冲进行计数。计数结果即与电容值成正比。该数据被锁存以保持显示稳定。此功能可由计数器集成电路(如CD4553三位BCD计数器)完成。

- 显示驱动与译码电路:将计数器输出的BCD码转换为七段数码管所需的驱动信号。常用集成电路如CD4511 BCD-七段锁存/译码/驱动器。

- 显示单元:三位七段数码管,用于直观显示电容值,单位通常为pF、nF或μF,可通过量程切换电路指示。

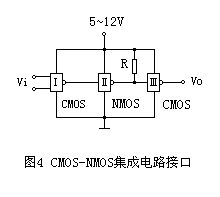

二、 关键集成电路设计与选型

- 电容-电压/时间转换IC:

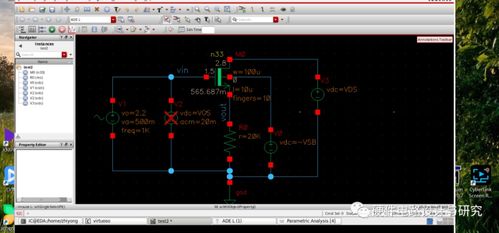

- 方案A(基于555):采用NE555定时器构成单稳态电路。设计时,基准电阻Rref需选用高精度、低温漂的金属膜电阻。输出脉宽 T ≈ 1.1 Rref Cx。该电路简单,但线性度和精度受555自身性能限制,适用于中低精度测量。

- 方案B(专用电容测量IC):如TLC555的改进型或专用的电容-数字转换芯片(如AD7745)。后者集成度更高,采用Σ-Δ转换技术,直接输出数字信号,精度和抗干扰能力显著提升,但成本较高。

- 计数器/逻辑控制IC:

- 核心芯片:CD4553是一款经典的三位BCD计数器,内部包含三个负沿触发的BCD计数器,并有多路扫描输出,可高效驱动三位数码管。其时钟输入(CLK)接收来自转换电路的脉冲,计数使能(DIS)由闸门时间信号控制,锁存(LE)和复位(MR)信号由时基控制逻辑生成。

- 译码驱动与显示IC:

- CD4511接收CD4553输出的BCD码,并将其译码后驱动共阴极七段数码管。它内部集成锁存器,可与CD4553的锁存信号配合,消除显示闪烁。

- 时基产生IC:

- 可采用晶体振荡器配合14级二进制分频器CD4060产生稳定的基准频率,再经后续分频得到所需的闸门时间(如由32768Hz晶振经分频得到2Hz信号,其半周期即为250ms的闸门时间)。

三、 工作流程与设计要点

- 测量周期:系统以固定周期工作。控制逻辑发出复位信号,清零计数器。开启精确的闸门时间(例如100ms),在此期间,由Cx决定的脉冲被送入计数器计数。闸门时间结束时,控制逻辑发出锁存信号,将计数值锁存至译码驱动器,并更新显示。之后,系统复位,准备下一次测量。

- 量程切换:为覆盖更宽的测量范围(如几pF到几百μF),需设计量程切换电路。可通过继电器或模拟开关切换不同阻值的基准电阻(Rref),或改变闸门时间,同时调整小数点显示位置。量程切换可由手动开关或自动量程转换逻辑实现。

- 校准与精度保障:

- 校准:使用高精度标准电容在特定量程进行校准,通过调整基准电阻或时基参数进行标定。

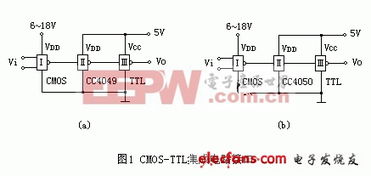

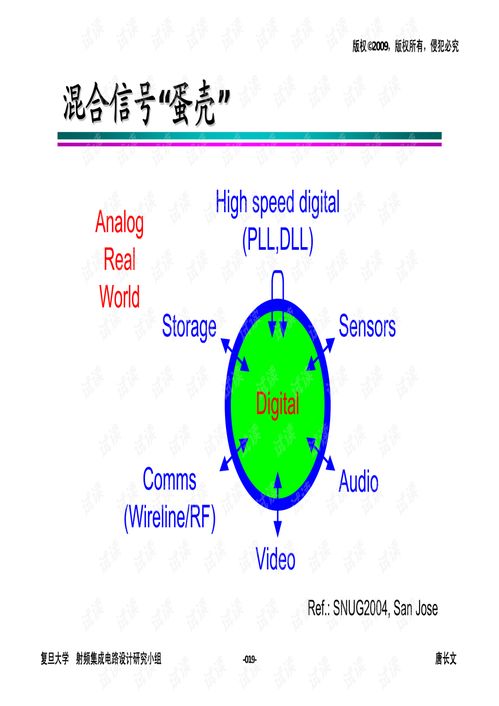

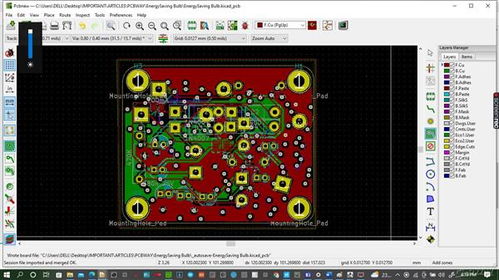

- 抗干扰设计:在转换电路输入端采用屏蔽和驱动保护,PCB布局时模拟与数字地线分开,最后单点连接,以减少噪声。

- 电源稳定性:为模拟转换部分提供稳定、低噪声的供电,关键部位可增加LC滤波或使用线性稳压器。

设计一个性能稳定的三位数字电容表,关键在于构建一个线性度好、稳定性高的电容-时间转换前端,并配以精准的时基和控制逻辑。采用CD4553、CD4511等经典数字集成电路可以构建出结构清晰、成本可控的系统。对于更高精度的要求,则需考虑使用集成电容数字转换器(CDC)的方案,将模拟信号处理全部集成于芯片内部,从而大幅简化外围电路设计并提升整体性能。

如若转载,请注明出处:http://www.datiantongchen.com/product/47.html

更新时间:2026-04-20 00:02:43